# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2011

# High Performance Geospatial Analysis on Emerging Parallel Architectures

Seth Warn University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Systems Architecture Commons

#### Recommended Citation

Warn, Seth, "High Performance Geospatial Analysis on Emerging Parallel Architectures" (2011). Theses and Dissertations. 156. http://scholarworks.uark.edu/etd/156

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

High Performance Geospatial Analysis on Emerging Parallel Architectures

# High Performance Geospatial Analysis on Emerging Parallel Architectures

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

By

Seth Warn Columbia College Bachelor of Science in Computer Science, 2006

> December 2011 University of Arkansas

#### **Abstract**

Geographic information systems (GIS) are performing increasingly sophisticated analyses on growing data sets. These analyses demand high performance. At the same time, modern computing platforms increasingly derive their performance from several forms of parallelism.

This dissertation explores the available parallelism in several GIS-applied algorithms: view-shed calculation, image feature transform, and feature analysis. It presents implementations of these algorithms that exploit parallel processing to reduce execution time, and analyzes the effectiveness of the implementations in their use of parallel processing.

| This dissertation is approved for recommendation to the Graduate Council. |

|---------------------------------------------------------------------------|

| Dissertation Director:                                                    |

| Dr. Amy Apon                                                              |

| Dissertation Committee:                                                   |

| Dr. John Gauch                                                            |

| Dr. Miaoqing Huang                                                        |

| Dr. Jackson Cothren                                                       |

# **Dissertation Duplication Release**

| I hereby authorize the University | of Arkansas Libraries to | duplicate this | dissertation v | when needed |

|-----------------------------------|--------------------------|----------------|----------------|-------------|

| for research and/or scholarship.  |                          |                |                |             |

| Agreed  |           |  |  |

|---------|-----------|--|--|

|         | Seth Warn |  |  |

| Refused |           |  |  |

|         | Seth Warn |  |  |

## Acknowledgements

I would like to thank the following people:

- Barbara Webb, my wife, for supporting me when I said "I think I'll go back to school," and in the years since then.

- Dr. Amy Apon, my advisor, for ceaseless support, encouragement, and advice.

- Stan Bobovych and Wesley Emeneker, for fruitful discussions and help with implementations and testing.

The work in this paper was supported in part by NSF grants #918970, #947679, and #072265.

# **Contents**

| 1 | Intr | duction                                                      | 1          |

|---|------|--------------------------------------------------------------|------------|

|   | 1.1  | Geospatial Applications Need Parallel Computing              | 1          |

|   | 1.2  | Target Applications                                          | 2          |

|   | 1.3  | Contributions                                                | 3          |

| 2 | Para | llel Computing                                               | 5          |

|   | 2.1  | Shared Memory Systems                                        | 5          |

|   | 2.2  | Distributed Memory Systems                                   | 7          |

|   | 2.3  | GPGPU                                                        | 8          |

|   |      | 2.3.1 CUDA                                                   | 9          |

|   |      | 2.3.2 Alternatives to CUDA                                   | 2          |

|   |      | 2.3.3 Applications of GPGPU                                  | 3          |

|   | 2.4  | Hybrid Clusters                                              | .3         |

| 3 | Viev | shed Analysis                                                | 5          |

|   | 3.1  | What is Viewshed Analysis?                                   | 5          |

|   | 3.2  | Viewshed Background                                          | 6          |

|   |      | 3.2.1 Brute Force and Approximate Methods                    | 6          |

|   |      | 3.2.2 The Planar Sweep Approach                              | 7          |

|   | 3.3  | A New Approach                                               | 9          |

|   |      | 3.3.1 Determining Visibility                                 | :0         |

|   |      | 3.3.2 Interpolation                                          | :3         |

|   |      | 3.3.3 Corrections for Earth's Curvature and Light Refraction | <u>'</u> 4 |

|   |      | 3.3.4 Integer Math                                           | 26         |

|   |      | 3.3.5 Planar Sweep                                           | :6         |

|   |      | 3.3.6 Optimized Status Structure                             | 28         |

|   |      | 3.3.7 Sweep Algorithm                                        | <u> 2</u>  |

|   |      | 3.3.8 Parallelization                                        | 4          |

|   | 3.4  | Experimental Results                                         | 5          |

|   |      | 3.4.1 Performance                                            | 5          |

|   |      | 3.4.2 Parallel Scaling                                       |            |

|   |      | 3.4.3 Offset Calculation                                     | 57         |

|   | 3.5  | Conclusion                                                   |            |

| 4 | Acc  | lerating SIFT on Hybrid Clusters 4                           | ŀ0         |

|   | 4.1  | What is SIFT?                                                | 0          |

|   |      | 4.1.1 Feature Detection                                      | 1          |

|   |      | 4.1.2 Feature Description                                    |            |

|   |      | 1                                                            | 4          |

|   | 4.2  | Parallelizing SIFT                                           |            |

|   |      | 4.2.1 Work Partitioning                                      |            |

|     |        | 4.2.2    | Octave File I/O                                     | 48 |

|-----|--------|----------|-----------------------------------------------------|----|

|     |        | 4.2.3    | GPU Acceleration                                    | 49 |

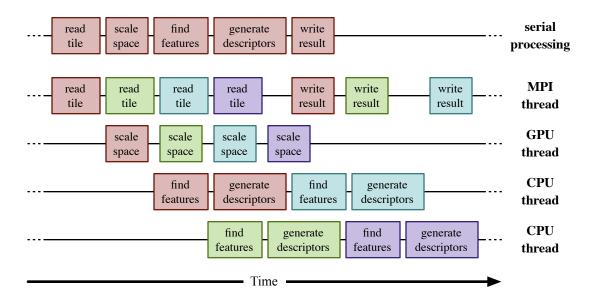

|     |        | 4.2.4    | Pipelined Concurrency                               | 50 |

|     | 4.3    | Experir  | mental Results                                      | 53 |

|     |        | 4.3.1    | Shared and Distributed Memory Scaling               | 54 |

|     |        | 4.3.2    | GPU Acceleration                                    | 59 |

|     | 4.4    | Conclu   | sions                                               | 60 |

|     |        | 4.4.1    | Future Work                                         | 61 |

| 5   | Circ   | ular Eai | rth Mover's Distance                                | 63 |

|     | 5.1    | Image l  | Registration                                        | 63 |

|     | 5.2    | Compa    | ring SIFT Features                                  | 67 |

|     |        | 5.2.1    | More on SIFT Feature Descriptors                    | 67 |

|     |        | 5.2.2    | Measuring Feature Dissimilarity                     | 68 |

|     | 5.3    | Implem   | nentation and Discussion                            | 71 |

|     |        | 5.3.1    | Experimental Setup                                  | 72 |

|     |        | 5.3.2    | Runtime of CEMD and L2                              | 73 |

|     |        | 5.3.3    | Initial Design: CPU-INITIAL and GPU-INITIAL         | 74 |

|     |        | 5.3.4    | Using Shared Memory: GPU-SHMEM                      | 75 |

|     |        | 5.3.5    | Optimizing Global Memory Reads: GPU-MEMOPT          | 75 |

|     |        | 5.3.6    | Reducing Shared Memory Bank Conflicts: GPU-INDEX    | 76 |

|     |        | 5.3.7    | Loop Unrolling: GPU-UNROLL                          | 78 |

|     |        | 5.3.8    | Algorithmic Improvements: GPU-FINAL and CPU-FINAL   | 79 |

|     |        | 5.3.9    | Performance Scaling                                 | 82 |

|     |        | 5.3.10   | Streaming Kernel Execution                          | 82 |

|     |        | 5.3.11   | Using Multiple GPUs on Multiple Machines            | 83 |

|     | 5.4    | Conclu   | sion                                                | 84 |

| 6   | Conc   | clusions |                                                     | 85 |

|     | 6.1    | Results  |                                                     | 85 |

|     | 6.2    | Applica  | ability of Parallel Computing to Given Applications | 86 |

| Bil | bliogr | aphy     |                                                     | 89 |

# **List of Figures**

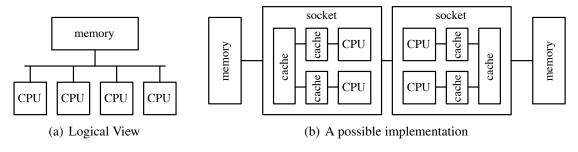

| 2.1  | Shared memory, as it is modeled and implemented                         | 6  |

|------|-------------------------------------------------------------------------|----|

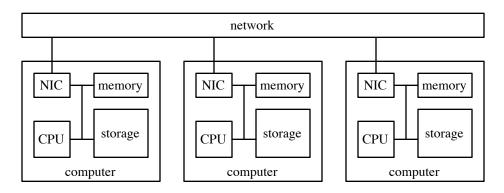

| 2.2  | A cluster computer                                                      | 8  |

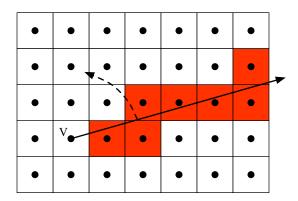

| 3.1  | A rotational planar sweep                                               | 17 |

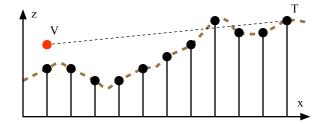

| 3.2  | Visibility between two points                                           | 20 |

| 3.3  | Interpolating heights over a raster DEM                                 | 22 |

| 3.4  | Component distances                                                     | 22 |

| 3.5  | Reusing interpolated values                                             |    |

| 3.6  | Correcting for Earth's curvature                                        | 24 |

| 3.7  | Ordering of samples around a viewpoint                                  | 27 |

| 3.8  | An implicit binary tree                                                 | 29 |

| 3.9  | The status structure used in this dissertation                          | 30 |

| 3.10 | Finding the maximum slope before $n$ in the status structure            | 31 |

| 3.11 | Using the event list and status structure to implement the planar sweep | 33 |

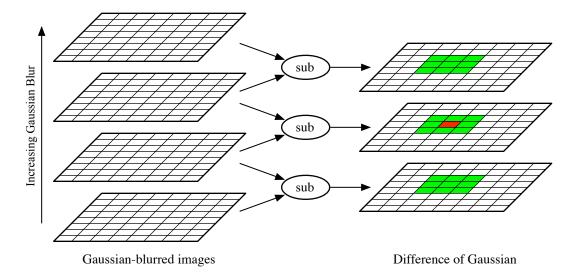

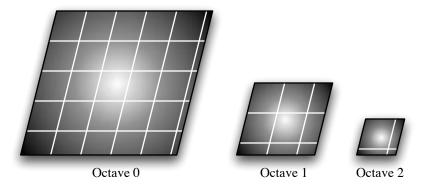

| 4.1  | Difference of Gaussian                                                  | 41 |

| 4.2  | Creating a SIFT descriptor                                              | 43 |

| 4.3  |                                                                         | 45 |

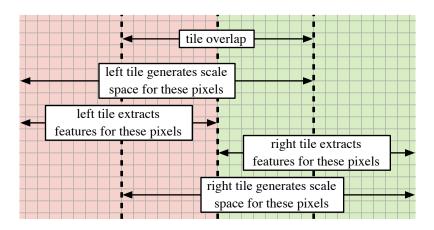

| 4.4  | Scale space partitioning                                                | 47 |

| 4.5  |                                                                         | 47 |

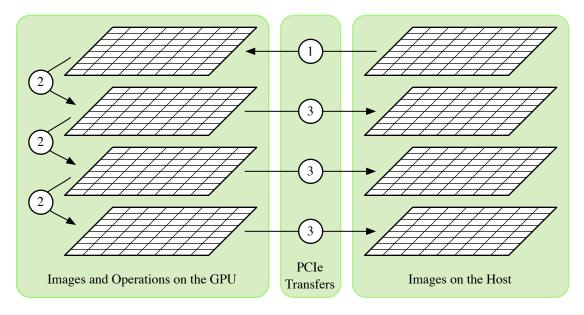

| 4.6  | Scale-space generation on GPU                                           | 49 |

| 4.7  | Concurrent task execution in SOHC                                       |    |

| 4.8  | Input image                                                             | 54 |

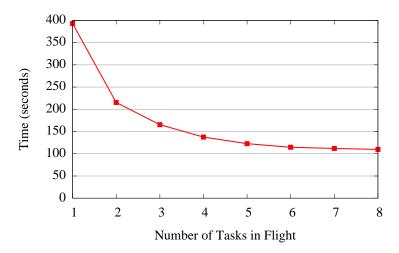

| 4.9  | Performance scaling with numbers of tiles                               | 55 |

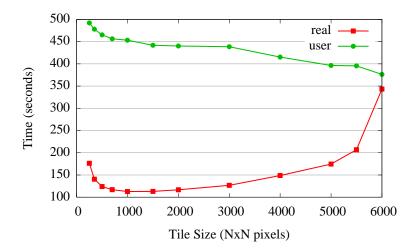

| 4.10 | How tile size affects processing time                                   | 57 |

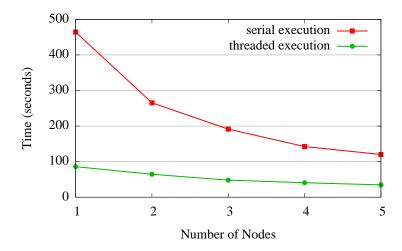

| 4.11 | Execution time of SOHC on a cluster                                     | 59 |

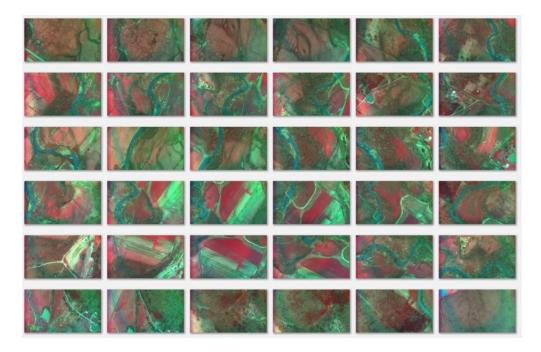

| 5.1  | Unorganized Block of Images                                             | 64 |

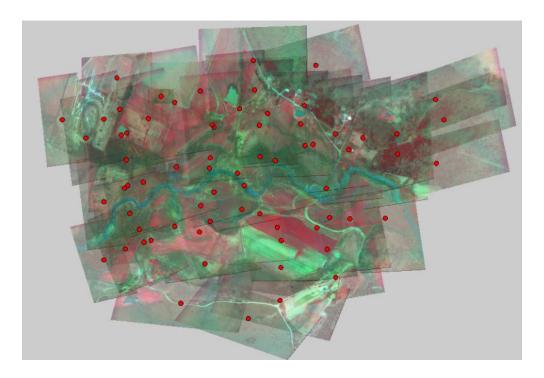

| 5.2  | Georeferenced Image Mosaic                                              |    |

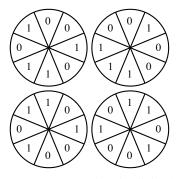

| 5.3  | SIFT Descriptors                                                        |    |

| 5.4  |                                                                         | 73 |

| 5.5  |                                                                         | 80 |

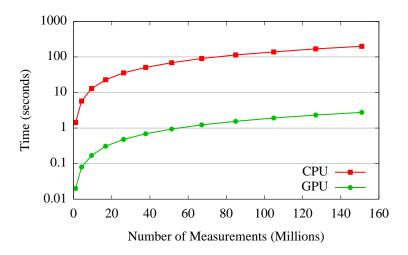

| 5.6  | Time to Complete $N$ Measurements                                       |    |

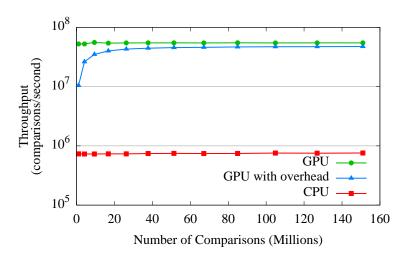

| 5.7  | Throughput of $N$ Measurements                                          |    |

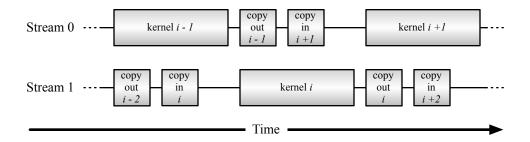

| 5.8  | Streaming Execution in CUDA                                             |    |

# **List of Tables**

| 2.1 | Comparing GPU and CPU performance                            | 9 |

|-----|--------------------------------------------------------------|---|

| 3.1 | Viewshed analysis: measured performance                      | 5 |

| 3.2 | Viewshed analysis: parallel scaling                          | 6 |

| 3.3 | Time to calculate and apply offsets for curvature correction | 7 |

| 4.1 | Breakdown of tile processing time                            | 6 |

| 4.2 | GPU-enabled tile processing                                  | 0 |

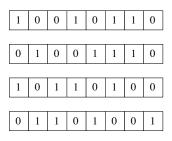

| 5.1 | CEMD Example with 4-bin Histogram                            | 1 |

|     | Performance of CEMD vs. Euclidean                            |   |

| 5.3 | CEMD Kernel Performance                                      | 4 |

#### Chapter 1

#### Introduction

#### 1.1 Geospatial Applications Need Parallel Computing

The term *geospatial* describes information that is spatially located relative to the Earth. This broad definition includes a wide range of data, such as historical temperature records, aerial and satellite photography, property records, and more. This data is frequently stored in *geographic information systems*, or *GIS*, which include both the spatially-referenced data as well as the hardware and software used to store, analyze, and display that data. Geospatial applications analyze this data to perform a variety of tasks, such as predicting how a disease will spread, or determining the optimal location for a new cell phone tower.

The increasing capacity of computers to store data, the expanding bandwidth of networks to transmit data, and the growing number and resolution of sensors collecting data result in an explosion in the amount of information processed by geospatial applications. Existing applications designed for serial computer architectures cannot handle this growth in data size, because advances in computer performance are now based primarily on increasing parallelism [1], rather than increasing single-thread performance.

Static single-thread performance will not limit the exponential growth of computational power; for example, single-rack servers capable of petaflop performance will be available in the next five to ten years [2]. However, this level of performance will be provided by massively multi-core processors, with hundreds of cores per chip. Existing tools written for serial architectures, or even tools written for parallel architectures with few cores, must be replaced with algorithms and software designed to take advantage of these new, massively-parallel computers.

Current multi-core chip architectures essentially replicate a small number of traditional CPU cores in a single package. However, the massively multi-core processors mentioned above will

evolve, at least in part, towards a more data-parallel, task-based parallel architecture [3] that is currently exemplified by GPU hardware, described in Section 2.3. Writing applications to take advantage of GPU accelerators provides performance benefits now, while making them compatible with HPC systems of the future.

## 1.2 Target Applications

The field of geomatics is concerned with a wide variety of problems. The problems addressed by this dissertation were chosen primarily because they are immediately useful to ongoing projects at the University of Arkansas Center for Advanced Spacial Technologies (CAST). Each has proven amenable to some form of parallelization.

**Viewshed analysis:** A problem in computational geometry whose answer is useful for a variety of geospatial research questions. Briefly, it uses a model of a given terrain to answer questions about line-of-sight for observers within that terrain. It is described further in Chapter 3.

**Feature Transformation:** A method in computer vision that attempts to convert raw input images into a list of important "features" which are more amenable to further analysis. This dissertation describes a well-known feature transformation algorithm, SIFT, and its implementation in Chapter 4.

**Feature dissimilarity:** The high-performance SIFT implementation described in Chapter 4 generates large amounts of data, consisting of billions of feature descriptions. A common analysis to perform on those features is to look for similar features derived from other images, which requires a method of measuring feature similarity. One such method is the Circular Earth Mover's Distance, or CEMD. This similarity measurement and its uses are described in Chapter 5.

#### 1.3 Contributions

The increase in the size of geospatial data sets requires faster tools to process that data, while the transition to parallel computer architectures means that existing tools, which are not designed for the new architectures, are not capable of the required performance. This dissertation describes an interdisciplinary project to create geospatial software tools capable of utilizing parallel computer architectures. This encompasses:

- 1. Examinations of the parallelism available in the three common geospatial applications listed above.

- 2. Software implementations of those applications designed to take advantage of the parallel architectures described in Chapter 2.

- 3. Evaluations of the effectiveness of said implementations.

These parallel implementations make it possible to use existing techniques on larger data sets, and enable the creation of new applications by making those techniques practical on a larger scale. Each of these implementations use novel methods to take advantage of parallel computers. In addition, the software developed has immediate applications, and is already used in geospatial research.

**Summary of results:** Each of the target applications is described in its own chapter; this is an overview of those results:

- Viewshed analysis is accelerated with novel algorithmic improvements and by exploiting

multi-core architectures. The speed of the resulting implementation, which can calculate a

16k×16k viewshed in 21 seconds on an inexpensive desktop computer, is orders of magnitude faster than available viewshed analysis software.

- SIFT feature extraction can benefit from all three forms of parallelism described in the next chapter: multi-core, cluster computing, and GPUs. The implementation described in Chapter 4 is a framework for SIFT and other scale-space based feature detectors, which uses a

novel partitioning and pipeline scheme to exploit these parallel architectures in a flexible manner. This is the only implementation of SIFT capable of operating directly on the very large images common in geospatial applications.

• Feature dissimilarity calculation is embarrassingly parallel, making it simple to use cluster computing for weak scaling. Chapter 5 focuses on the details of extracting performance from individual GPUs, and the resulting implementation is shown to be nearly optimal. The GPU code is embedded in an application that uses hybrid clusters to enable CEMD calculation for large numbers of features.

#### Chapter 2

#### **Parallel Computing**

Parallel computing refers to wide variety of computing systems where multiple calculations occur at the same time. It includes both parallel computer architectures [4], and the programming models, languages, and APIs (application programming interfaces) used to write software that operates on parallel architectures. This is an enormous topic, and discussing it is made more difficult by the insufficiency of accepted terminology, for example Flynn's Taxonomy [5], to describe modern parallel systems, as well as disagreement over the definitions of such basic terms as parallel and concurrent. Therefore, this chapter restricts its description of parallel computing to only those architectures and software constructs directly relevant to the applications presented in later chapters.

## 2.1 Shared Memory Systems

Parallel computers may be divided into two groups, according to the configuration of their memory. The first group are *shared memory* computers; as the name suggests, all processing elements have shared access to the computer's memory. The most common examples of these are *symmetric multiprocessing*, or SMP, computers, where multiple identical CPUs are connected to a common system memory and controlled by a single operating system. The CPUs may be together in a single package and share a single motherboard socket, or they may be distributed among several sockets.

**Threaded Programming:** The canonical method of programming in order to take advantage of SMP systems is *threaded programming*. This is not, strictly speaking, a parallel programming model. Instead, some number of *threads*, which are sequences of instructions like a serial program, that share access to resources such as memory, and that execute *concurrently*: each thread proceeds independently of the others. This may be implemented by executing instructions from each thread in an interleaved fashion on a single CPU, or simultaneously executing instructions from multiple

Figure 2.1: Shared memory, as it is modeled and implemented

threads on several CPUs. This nondeterminism is managed with a variety of constructs, such as mutexes, semaphores, and monitors.

POSIX threads [6] are a widely-used C API for threaded programming. Other APIs, such as Java threads [7], Boost/C++ threads [8], or Windows threads [9], allow similar operations. These APIs present a very simple abstraction of the underlying architecture, as shown in Figure 2.1(a): each CPU has equal access to a shared memory pool, thus the physical site of thread execution is irrelevant. A somewhat more realistic, but still simplified, depiction of an SMP system is shown in Figure 2.1(b). This system shows how threads may not have equal access to memory resources, and how thread placement may affect thread execution, for example by sharing cache resources. The effect on execution time can be significant [10]; libraries such as libNUMA [11] allow control over these sorts of execution details.

Alternatives to Threads: The threaded programming model mimics the shared-memory architecture, and is therefore natural, but is often difficult to use correctly [12]. A number of methods have been designed to make using shared memory systems easier. One of the most widespread is OpenMP [13], an API for C, C++, and Fortran. Typical OpenMP programs will not explicitly create a number of threads. Instead, the programmer specifies that some operation, such as a reduction or the iterations of a loop, should be done in parallel. The OpenMP will distribute this work to multiple threads to take advantage of multiple CPUs, but this is transparent to the programmer, who is thus freed from much of the concurrency management required in threaded programming.

A common pattern in threaded programming is the thread pool. In a thread pool, there are

a number of threads, typically equal to the amount of physical parallelism available, that is, the number of CPUs. The parallel application is broken into a number of *tasks*, which are units of work than can be performed concurrently. Typically, there are far more tasks than threads, an they will be stored in queues. Each thread dequeues tasks, completes them, and dequeues another task, until the pool of tasks is exhausted. Creating and destroying threads typically incurs significant operating system overhead; task queueing and dequeuing is typically far faster. This allows parallelism to be specified at a relatively fine level.

Instead of manually implementing thread pools, programmers can take advantage of libraries and compiler extensions that, like OpenMP, handle implementation details, allowing the programmer to simply specify the parallelism in the code. Cilk [14] was an early example of this approach, now commercialized as Cilk Plus [15]. More recent examples include Intel's Thread Building Blocks [16], Apple's Grand Central Dispatch [17], and Microsoft's Task Parallel Library [18]. Concurrent languages like Google's Go [19] allow specification of task-level parallelism with built-in language constructs.

#### 2.2 Distributed Memory Systems

In contrast to shared memory systems, where all processors have access to the same memory, distributed memory describes a system where each processor has access to a private memory. In a distributed memory system, accessing memory other than the processor's own private memory requires communication with another processor. A common example of distributed memory is the computer *cluster*, shown in Figure 2.2: a collection of computers, typically linked by a high-speed local network, and working closely together.

The Message Passing Interface [20], or MPI, is the *de facto* standard for cluster programming. As with threaded programming, computation is specified as a set of instruction sequences running concurrently, with a number of mechanisms for synchronization. These sequences are called *processes*; it is usual for each process in an MPI application to be running identical code, so MPI is sometimes called *SPMD*, or single-program, multiple-data. Like OpenMP, the programmer typi-

Figure 2.2: A cluster computer

cally does not specify a number of processes at compile time; and will instead write partitioning logic that detects the number of processes at runtime and divides work among them. MPI is an API that handles the management of, and communication between, these processes.

The division between shared memory systems and distributed memory system is not blackand-white. In modern clusters, there are multiple CPUs per compute node, which share memory

within the node, but not with CPUs on other nodes. Frequently this is simply ignored; a single

MPI process is created for each CPU, and the underlying MPI runtime may or may not optimize

communications between processes executing on the same node. Shared memory and messagepassing may also be explicitly combined, for example, by launching a single MPI process per node,

then using OpenMP in each process to exploit the multiple CPUs in each node.

Another approach is to represent the collective memory resources of the cluster as a single, non-uniform memory, called a *partitioned global address space*, or PGAS. This programming model is the subject of ongoing research, and is used by a number of languages such as X10 [21] and Chapel [22].

#### 2.3 GPGPU

Dedicated graphics processing hardware has existed for many years. Computer chips designed solely to handle graphics are called GPUs, or graphics processing units. GPUs exist in many forms; they are integrated with CPUs and other hardware in systems-on-chip designed for mo-

Table 2.1: Comparing GPU and CPU performance.

|            | NVIDIA GeForce 580 | Intel Core i7 950 | Intel Core i7 970 |

|------------|--------------------|-------------------|-------------------|

| $GFLOPS^a$ | 1581               | 98.2              | 154               |

| $Price^b$  | \$500              | \$300             | \$900             |

| TDP        | 244 W              | 130 W             | 130 W             |

| Memory BW  | 192 GB/s           | 25.6 GB/s         | 25.6 GB/s         |

| GFLOPs/\$  | 3.16               | 0.33              | 0.17              |

| GFLOPs/W   | 6.48               | 0.76              | 1.18              |

|            |                    |                   |                   |

<sup>&</sup>lt;sup>a</sup> Theoretical peak, single-precision, multiply and add

bile computing, as separate chips on a motherboard, and most commonly as daughterboards that combine a GPU, dedicated video memory, and video output hardware, called video cards.

The last decade has seen growing interest in the use of these video cards for non-graphical computation. This usage is now called GPGPU, or general-purpose computing on GPU. The rising popularity of GPGPU is due to the impressive performance of GPU processors, both in absolute terms and in relative efficiency. Table 2.1 above shows high-end, consumer-oriented GPU and CPU parts from NVIDIA and Intel, respectively. This sort of direct comparison ignores many important details, and even limited GPU–CPU comparisons are notoriously difficult; however, the order-of-magnitude differences in performance-per-dollar and performance-per-watt have driven widespread and growing adoption of GPUGPU programming.

#### 2.3.1 CUDA

The Compute Unified Device Architecture, or CUDA, is a parallel architecture [23, 24] and programming model [25] designed by the NVIDIA corporation and implemented in their GPU product line. NVIDIA also provides a language called "C for CUDA" [26], compiler, and libraries used to program their GPUs; these are often informally referred to as part of CUDA.

Developing CUDA was NVIDIA's response to an already-active GPGPU programming community. While instances of using repurposed graphics hardware can be found going back many years, the current form of GPGPU programming began after 2000 with the addition of programmable shaders to commodity video cards. Programmers discovered that they could encode non-graphics

<sup>&</sup>lt;sup>b</sup> As of January, 2011

problems as pixels and shader operations using shader languages like OpenGL's GLSL or Microsoft's HLSL and execute them on a GPU. This proved useful but tedious, and by 2004, several higher-level languages [27, 28] had emerged. These languages looked more like traditional C or C++ and were compiled into shader code. NVIDIA released CUDA in early 2007 and has since release several updates to add features requested by the GPGPU community.

**Programming Model:** CUDA applications are based on the execution of kernels on the GPU device. The kernels are defined using C/C++ and are executed many times in parallel; each kernel instance is called a thread in CUDA, although these threads are not the same as POSIX-style threads. Like other SPMD models such as MPI, the threads have access at runtime to a unique identifier, called the "thread ID" in CUDA. The threads are grouped in a programmer-specified hierarchy, with the hundreds of threads grouped into blocks and potentially thousands of blocks grouped into a grid.

The thread hierarchy is a convenient way to organize execution: both the blocks and grids can be one-, two-, or three-dimensional to suit the needs of the application. Thread blocks are also reflected in CUDA's execution model and memory hierarchy. First, threads can use lightweight synchronization mechanisms to cooperate with other threads in the same block, but the blocks must be able to execute independently. Second, threads have access to a small, fast pool of memory, called "shared memory," that is visible to all threads in their block, and only persists for the duration of the block's execution.

Shared memory is one of several types of memory in the CUDA model. Global memory is the other primary memory pool, which is visible to all blocks, and is much larger and slower than shared memory. While researchers have implemented barriers [29] and work queues [30] at the grid level, CUDA has no built-in mechanism for grid-level synchronization, so each block will typically write to a separate region of global memory. Threads may either explicitly copy data between these memories, or the shared memory can act as a cache. There are another two memory types, constant and texture memory, that are read-only to threads and are used for more specialized

purposes.

The global memory pool is also the only memory accessible to the "host," the computer running the CUDA-accelerated application. The typical execution path of a CUDA program involves some host code execution, copying input data from the host memory into the CUDA device's global memory, and launching a kernel. The results of kernel execution are placed back into global memory, then copied into the host's memory, which proceeds with normal execution. These copies typically take place over a PCIe bus, which has far less bandwidth than the memory systems of the host or device, and minimizing these host–device copies is a primary design concern for CUDA developers.

Architecture and Optimization: The implementation of CUDA hardware depends heavily on data parallelism and latency-hiding, which affects how CUDA programs are written. CUDA GPUs consist of a number of streaming multiprocessors, or SMs, each of which has a number of instruction-locked processors called "CUDA cores." Nvida describes the CUDA architecture as "Single Instruction Multiple Thread," or *SIMT*. All threads in a block execute on the same SM; the instruction-locked cores mean that divergent behavior among threads in a block is simulated by masking off operations on some cores. This means that avoiding divergence is another design priority for developers.

The global and shared memory pools have their own quirks, as well. For example, the shared memory is arranged in a series of 32 banks, each of which can be accessed in parallel. The address space is striped across these banks in four-byte words; writes to the same bank are serialized. Data structures and algorithms must be designed to avoid these "bank conflicts." The global memory has its own set of rules governing which memory operations can occur in parallel, "coalescing" the operations into a single memory transaction. The performance penalty associated with suboptimal memory access patterns means that data structures must be carefully considered when writing GPU kernels, and additional computational work may be offset if it leads to better access patterns [31].

Typically, far more threads are resident on an SM that are currently executing. Each SM can

switch threads without any overhead; this mechanism is used to hide the latency of memory operations, and even regular instructions [32, 26]. Maximizing the architecture's ability to hide latency, by avoiding synchronization instructions and tuning the number of threads in a block, is another important design consideration for CUDA applications.

#### 2.3.2 Alternatives to CUDA

Currently, CUDA is the most commonly-used GPU framework for high-performance computing. OpenCL [33] is a popular and growing alternative which defines a language and programming model similar to CUDA, but is vendor-agnostic. Code written using OpenCL is typically somewhat slower than code using CUDA [34]. Microsoft has also released their own framework, DirectCompute, as part of their DirectX [35] family of APIs. PGI's CUDA Fortran [36] replaces the C for CUDA language with a Fortran-based equivalent.

Some alternatives seek to add a level of abstraction above CUDA, rather than replace it. The Thrust [37] project is a C++ template library that allows the creation of CUDA code using data-parallel primitives, such as scan, sort, or reduce, with interfaces similar to the C++ STL (standard template library). The *hi*CUDA [38] language uses C pragmas and a source-to-source compiler to automatically handle some CUDA programming tasks. OpenMPC [39] also uses pragmas, building on OpenMP, to accomplish the same goal. Other alternatives run CUDA on a different underlying architecture, such as an FPGA [40, 41] (field programmable gate array), or even traditional x86 CPUS [42].

Other threaded, data-parallel architectures have been created in response to flat single-thread performance. AMD's Accelerated Parallel Processing (APP) framework [43] for GPGPU is the closest equivalent to CUDA. IBM's Cell [44] and Intel's Larrabee [45] both combine a large number of simple CPUs with wide vector units. Both AMD and Intel have started producing desktop CPUs that integrate GPU cores [46, 47], and Intel's AVX [48] is increasing the SIMD capabilities of their desktop CPUs. Several studies have compared performance among the architectures [49, 50].

## 2.3.3 Applications of GPGPU

Given the high FLOPs (floating point operations per second) capacity of GPUs and their data-parallel architecture, many have used GPUs for linear algebra and dense matrix operations. CUBLAS [51] and MAGMA [52] implement a CUDA-accelerated BLAS interface which can be used with HPL [53]; while the raw performance is impressive, the efficiency (measured flops vs. theoretical peak) is lower than CPU-based clusters [54, 55]. Sparse matrix operations have also been accelerated by finding data structures that efficiently encode such matrices for GPU processing [56, 57].

GPUs are being used for a wide variety of other applications. These range from sorting [58] and FFT (fast Fourier transform) calculation [59] to biomolecular simulation [60], sequence alignment [29], and quantum chromodynamics [61]. As GPUs become more common, they are also being used in non-HPC applications such as real-time systems [62] and databases [63].

## 2.4 Hybrid Clusters

Cluster computers and GPUs are both attractive platforms for high-performance computing due to their low price/performance ratios. Early GPU-equipped clusters [64] predate CUDA, but are identical to modern hybrid clusters in configuration. Where a typical cluster is group of commodity server nodes, frequently connected by a high-performance interconnect, a hybrid cluster attaches one or more GPUs to each node as daughterboards connected via the PCIe bus.

This model of normal-computer-plus extends to programming these clusters, as well. The GPUs cannot communicate directly with other GPUs, even on the same node, so hybrid-cluster applications function essentially identically to other cluster applications. They will typically use MPI; the individual MPI processes will accelerate selected functions on a GPU. Because moving data from GPU to GPU must always involve copying from a GPU, to a CPU, then a network transfer, then another CPU to GPU transfer, minimizing communication and hiding communication latency are even more important to hybrid applications than other cluster software. MPI libraries and cluster scheduling software are still largely GPU-agnostic, which causes some difficulties [65],

but these systems are being updated to be GPU-aware.

The TSUBAME computers in Japan were some of the first to adopt GPU use for large, production compute clusters — TSUBAME 1.2 was the first GPU-equipped cluster on the TOP500 list, in 2008. Now, TSUBAME 2.0 is one of the three GPU-equipped computers in the of the top five systems listed by TOP500 [66].

Hybrid clusters are being applied to a range of computing problems, starting with basic tools such as Linpack [55], and on to N-body simulation [67, 68, 69], molecular dynamics [70], weather simulation [71], and more. These authors all report that the design considerations of typical GPGPU programming, such as minimizing PCIe communication, remain important; several also emphasize the importance of overlapping GPU and CPU computation, so that the considerable CPU power of these clusters is not wasted.

The term "hybrid clusters" applies not only to GPU-equipped clusters, but to any cluster that executes code on more than one type of architecture. Like the GPU clusters above, these computers will usually have CPU-equipped nodes with one or more accelerators. The most well-known is Roadrunner [72], which use Cell processors in addition to AMD CPUs. Other accelerators have been used, such as FPGAs [73] and specialized floating-point accelerators from ClearSpeed, which were also used in TSUBAME.

## **Chapter 3**

#### **Viewshed Analysis**

This chapter describes a new viewshed analysis algorithm, and a parallel implementation of that algorithm. Viewshed analysis is described in Section 3.1, while the rest of the chapter describes the new algorithm; an implementation of it named "pvshed," made as part of this dissertation; and the performance of pvshed.

The new implementation described here is orders of magnitude faster than previous viewshed analysis software. This speedup is partially due to algorithmic improvements; additionally, pvshed can take advantage of the SMP systems described in Section 2.1. This additional speed is useful, both to allow current analysis methods to complete in reasonable times on larger data sets, and to enable the development of new algorithms that require repeated viewshed analysis, which are impractical with slower viewshed analysis.

#### 3.1 What is Viewshed Analysis?

A *viewshed* is the terrain visible from a fixed viewpoint: "If I stand here, what can I see?" Viewshed analysis has many applications: placement of communication [74] or radar facilities [75, 76], which require good visibility; calculating the "zone of visual influence," areas where a development will have a visual impact; designing nature trails for maximum visibility [77, 78]; correcting aerial or satellite imagery for illumination variances [79]; and finding the fewest required observers to watch a given terrain [80] are among its uses.

Viewshed analysis processes a *digital elevation model*, or DEM, to determine the viewshed from a given viewpoint. DEMs are typically in one of three forms: Triangulated irregular networks, or TINs; *heightmaps*, also called raster or grid DEMs; and contours [81]. Heightmaps store elevation data for a terrain in a regularly-spaced array of samples, and are more common in modern geographic information systems (GIS) applications. The expansion of remote sensing

technologies is creating ever-growing amounts of DEM data. For example, the National Elevation Database [82] provides raster DEM data at 30-meter resolution or finer for the entire continental United States. LIDAR (light detection and ranging) uses laser pulses to measure range to a target; satellite- or aircraft-mounted LIDAR is now providing DEM data at 1-meter and even sub-meter resolution.

Strictly speaking, viewshed analysis calculates a boolean answer for each height sample, visible or obstructed, and may be represented by a matrix of single bits that correspond to the terrain samples. However, GIS systems are typically interested in not just a boolean answer, but the *maximum obscured height*; that is, how tall a pole can be placed at that point on the terrain and still be unseen from the viewpoint? Because visibility is bidirectional, viewshed analysis can also be used to answer the converse of the original question: "If I stand here, what can see me?"

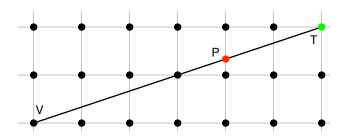

#### 3.2 Viewshed Background

The viewshed analysis problem was described at least as early as 1986 [83], and applications of viewshed analysis were explored over several years [84, 85]. In these papers, TIN models were preferred. Over time, the heightmap became the preferred form for DEMs. The viewshed for a grid DEM is as follows: The DEM defines the input terrain and consists of a set of height samples. Each sample is a three-dimensional point, and the samples are spaced in a regular grid above the xy plane. The viewshed is the set of all the height samples visible from the viewpoint. There are varying methods of determining visibility between two points, but in general, a target point T is visible to a viewpoint V if no part of the terrain intersects the line segment  $\overline{VT}$ .

## **3.2.1** Brute Force and Approximate Methods

The most straightforward approach to viewshed analysis of heightmaps is simple; visibility for each sample point is determined by checking all height samples between the viewpoint and the target sample point. If and only if all intervening samples are below the *sightline* connecting the viewpoint and the target, the target is visible. For a terrain S with  $n \times n$  samples, this is an  $O(n^3)$

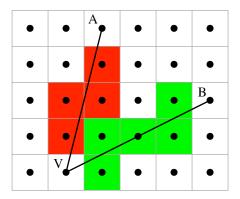

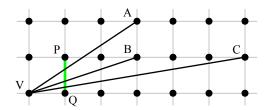

Figure 3.1: The planar sweep described by van Krevald. Looking down onto the terrain, a half-line is rotated around the viewpoint V. Pixels (shown in red) that intersect the line are stored in the status structure, ordered by distance from the viewpoint.

algorithm: for each of the  $n^2$  samples, O(n) intervening samples between the viewpoint and the target sample must be checked.

Because the brute force approach requires a great of computation time, several authors explored approximate methods. The Xdraw method [86] was highly influential. It operates by growing a "ring" of line-of-sight information around the viewpoint; the sightline to a target is determined by interpolating between the two samples immediately closer to the viewpoint. This approach has the disadvantage of diffusing irrelevant information — through repeated interpolation, samples far from the sightline contribute to the line-of-sight determination.

#### 3.2.2 The Planar Sweep Approach

Later, van Krevald described [87] how to perform viewshed analysis in  $O(n^2 \lg n)$  time using the planar sweep concept from computational geometry. The new approach described later in this chapter is also based on the planar sweep. Van Krevald considered the height samples as the centers of square pixels, as shown in Figure 3.1. Conceptually, van Krevald's algorithm rotates a half-line around the viewpoint in a full circle. The pixels beneath the sweep line are stored in a status structure, added as the sweep line first intersects the pixel, then removed as the sweep line leaves the pixel. The status structure is used to determine the visibility of each pixel; this is described in more detail, below.

The Status Structure: Key to this method is the use of a self-balancing binary search tree, such as a red-black tree, as a status structure to track the cells pixels under the sweep line. The pixels are ordered within the tree by their distance from the viewpoint. A node in the tree stores a single pixel. The tree is augmented by associating an extra number with each node. For the leaf nodes, this number is the slope from the viewpoint to the height sample represented by the event stored at that node. For internal nodes, the number stored is the maximum of the two slopes stored by its two children. These numbers are updated bottom-up after each update, so that internal nodes will always store the maximum slope of their subtree, and any update takes  $O(\lg n)$  time.

This augmentation allows van Krevald's status structure to answer visibility questions in  $O(\lg n)$  time. The tree is ordered so that leftmost events are closer to the viewpoint. During tree traversal, each time the right child is chosen, the left child is the root of a subtree whose members are all closer to the viewpoint. Each of these left child nodes records the maximum slope of its subtree, and there will be at most  $O(\lg n)$  left nodes during tree traversal. The maximum of these values is the greatest slope between a target point and the viewpoint. This greatest slope can be used to determine visibility: the product of the slope and the horizontal distance to the target is the maximum obscured height at the location of the target. This is discussed in more detail in Subsection 3.3.1.

**The Sweep:** Using the status structure, van Krevald describes the sweep algorithm as follows:

- 1. Each sample is considered the center of a pixel. For each pixel, record three events: an "add" event at the point when the sweep line first crosses the pixel, a "search" event when the point when the sweep line crosses the center of the pixel, and a "remove" event at the point when the sweep line leaves the pixel. There are  $n^2$  pixels, which means there are  $3n^2$  events; listing these events takes  $O(n^2)$  time.

- 2. The angle of each event is measured between a line defined by the viewpoint and the event, and a line parallel to the x-axis intersecting the viewpoint. Sort the events by their angle; sort events with the same angle by distance from the viewpoint. This has the effect of listing all events as they appear from the viewpoint, turning counter-clockwise. Sorting the  $3n^2$  events

takes  $O(n^2 \lg n)$  time.

3. Simulate the planar sweep by repeatedly removing events from the beginning of the list and processing them. When processing "add" or "remove" events, the pixel in question is added or removed from the status structure as described above. Processing a "search" event corresponds to the sweep line passing directly over the center of a pixel. As the sweep line crosses the center of pixel P, the status structure stores all the pixels between the viewpoint and P, and the maximum intervening slope is used to determine the visibility of P. Each of the  $3n^2$  events requires a  $O(n^2)$  status structure operation, so the sweep takes  $O(n^2 \lg n)$  time.

The three phases of the algorithm, listing events, sorting events, and processing events, take  $O(n^2)$ ,  $O(n^2 \lg n)$ , and  $O(n^2 \lg n)$  time, respectively. The combined execution time is also  $O(n^2 \lg n)$ .

Van Krevald did not implement his algorithm, and several authors continued to explore alternatives, such as approximate methods [88, 89, 90, 91, 92] or GPU acceleration [93]. However, some work [94, 95, 96] has used the rotational-sweep approach while focusing on minimizing I/O operations for large DEMs.

#### 3.3 A New Approach

The new viewshed analysis algorithm described in this chapter is based on the planar sweep and shares the  $O(n^2 \lg n)$  runtime for  $n \times n$  grid DEMs. However, it uses a number of techniques to increase performance. First, it avoids the use of computationally-expensive trigonometric and square root functions to determine visibility and for the planar sweep, as described in Subsection 3.3.1 and Subsection 3.3.5, respectively. Second, it uses a status structure, described in Subsection 3.3.6, which is optimized for for visibility calculations on grid DEMs. Third, it parallelizes the viewshed computation, as described in Subsection 3.3.8, to take advantage of SMP computers.

Figure 3.2: Calculating visibility of T from viewpoint V. The original terrain is shown in profile as a heavy dashed line; the terrain is represented as an array of height samples, shown as black dots.

#### 3.3.1 Determining Visibility

Approaches to viewshed analysis vary in how they determine the visibility of a target point from the viewpoint. The method used in this chapter is described below, starting with a simplified version where the xy-projections of the viewpoint, target, and height samples are all collinear, then generalizing to visibility over a two-dimensional grid.

**Simplified Visibility:** Consider determining the visibility of a target point T from a viewpoint V. Figure 3.2 shows an example where T is not visible from V, because the line segment  $\overline{VT}$ , also known as the *sightline*, intersects the terrain between V and T. In general, T will be visible if and only if all samples between V and T are below the sightline.

This condition can be verified by comparing the slope of  $\overline{VT}$  with the slope from V to the intervening samples. T is visible from V if and only if

$$\frac{T_z - V_z}{T_x - V_x} > \frac{S_z - V_z}{S_x - V_x}$$

for all samples S such that  $V_x < S_x < T_x$ . To perform this comparison, many viewshed algorithms will first calculate the angle of the slopes using the arctangent, then compare the values of the slopes. In effect, this is determining the result of the above comparison by evaluating:

$$\arctan\left(\frac{T_z - V_z}{T_x - V_x}\right) > \arctan\left(\frac{S_z - V_z}{S_x - V_x}\right).$$

However, the arctangent is a computationally expensive function, and there is no need to obtain the angle of the slope. The approach in this chapter avoids using the arctangent by storing the slopes as a rational data type; that is, it simply stores the vertical and horizontal differences. Slopes stored in this fashion can be compared by cross-multiplying:

$$(T_z - V_z) \times (S_x - V_x) > (S_z - V_z) \times (T_x - V_x).$$

The actual angle of the slope is never calculated.

If the maximum of all the intervening sample slopes is known, then visibility can be determined with a single comparison. If the sightline is above the intervening sample with the greatest slope, it will also be above all other intervening samples. Also, the maximum intervening slope can be used to calculate the obscured height at a target; for a maximum slope m, the obscured height h at  $T_x$  is determined by

$$h = V_z + m \times (T_x - V_x) - T_z. \tag{3.1}$$

Visibility Over a Grid: Computing visibility over a grid of height samples adds complexity, because the sightline does not usually pass directly over intervening samples. This raises two questions: what points along the sightline should be checked to see if the obstruct the sightline, and what height values should be used at those locations? Here, it is useful to compare to van Krevald's approach, shown in Figure 3.3(a). He considered each sample point to be the center of a square cell. If the line segment  $\overline{VT}$  crosses a cell with center P and the slope of  $\overline{VP}$  is greater than the slope of  $\overline{VT}$ , then T is not visible from V.

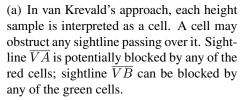

In contrast, Figure 3.3(b) illustrates the strategy used in this chapter. It checks for obstructions where the xy projection of the sightline intersects the sample gridlines. For a given sightline, only intersections with either x- or y-gridlines are checked, choosing based on which results in the greater number of checks. Put another way, checks are performed at grid intersection along the longest axis of the sightline. Where the intersection with a gridline coincides with a sample, as occurs at P, the sample height is used to check for obstruction. However, in most cases the

(b) Top-down view of example sightlines  $\overline{VA}$  and  $\overline{VB}$ . Intervening values are interpolated between the pairs of samples marked in red for  $\overline{VA}$  and green for  $\overline{VB}$ . No interpolation is required at P, where the sightline passes directly over a height sample.

Figure 3.3: Interpolating heights over a raster DEM

intersection with a gridline will occur between two samples. In this case, a height is interpolated based on those two points, which are the nearest neighbors along the gridline. The interpolation method is discussed in Subsection 3.3.2.

Determining the true slope of a line segment over a grid requires calculating the Euclidean distance between sample points. Consider Figure 3.4: the slope of  $\overline{VP}$  is

$$m_{\overline{VP}} = \frac{P_z - V_z}{\sqrt{(P_x - V_x)^2 + (P_y - V_y)^2}}.$$

Comparing  $m_{\overline{VP}}$  and  $m_{\overline{VT}}$  to determine visibility requires multiple uses of the square root function and is computationally expensive. Since the objective is only to compare the slopes, not to determine their actual values, only comparing the x- or y-components of the slopes is required.

Figure 3.4: Component distances

For example, the x-components of the slopes can be compared using

$$\frac{P_z - V_z}{P_x - V_x} \stackrel{?}{\geq} \frac{T_z - V_z}{T_x - V_x}.$$

This correctly determines which slope is greater, while using considerably less arithmetic.

## 3.3.2 Interpolation

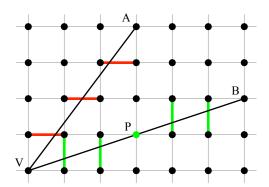

When a line of sight passes between two sample points, some form of interpolation is necessary. This chapter uses one of the simplest possible methods, the minimum function: the height between two neighbors is considered to be level with the lowest of those neighbors. This has several advantages. First, determining the minimum is computationally inexpensive, while also obviating any need to calculate the distance to the neighbors. Figure 3.5 demonstrates the second and more important advantage: all sightlines passing between two neighbors can reuse the same interpolated value.

Using minimum-based interpolation may seem like an oversimplification, but it is practical. Where interpolation occurs far from the viewpoint, or where there is a small difference between neighbors, the choice of interpolation method will make little difference in the viewshed. Where there are dramatic differences in elevation near the viewpoint, the interpolation method can make a large difference, but no interpolation method is guaranteed to be more accurate. The choice of minimum is meant to be conservative: any point that is found to be hidden is more likely to be hidden. The maximum function may be used instead, to bias the analysis so that visible points are

Figure 3.5: Sightlines  $\overline{VA}$ ,  $\overline{VB}$ , and  $\overline{VC}$  all require an interpolated value between P and Q. Interpolating using the the minimum of the heights at P and Q, all three can use the same value.

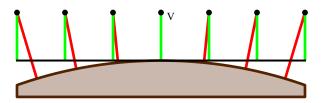

Figure 3.6: Correcting for Earth's curvature: The original heights, in red, are relative to the surface of the Earth. These heights are mapped to new heights, in green, relative to a plane tangent to the surface of the Earth at the viewpoint.

very likely to be visible. A rough margin of error can be established by performing the analysis twice, once with each method [86].

#### 3.3.3 Corrections for Earth's Curvature and Light Refraction

Viewshed as described above considers the input heightmaps as a set of heights above a plane. In reality, height samples are relative to the curved surface of the Earth. For some applications, the error introduced by ignoring the Earth's curvature will be acceptable; the controlling factors are the accuracy required by the application and the maximum view distance. At one kilometer, the vertical error is 7.8 cm; at 16 km, the vertical error is 20 m.

For applications where this error is not acceptable, planar viewshed models can still be used. The heights relative to the surface of the Earth are mapped to height relative to the surface of a plane tangent to the Earth directly beneath the viewpoint. This is illustrated in Figure 3.6 and uses several approximations:

- The Earth is modeled as a sphere of radius R, where R=6371 km. The accuracy of this approximation is discussed elsewhere and beyond the scope of this paper.

- The distance between samples along the plane is considered equal to the distance along the surface of the Earth. For a horizontal distance from the viewpoint of 16 km, this translates to a horizontal error of less than 3.4 cm.

Practically, this process takes an input heightmap and produces a new heightmap where samples further from the viewpoint are lower, simulating Earth's curvature. Viewshed calculation can proceed as if all heights are relative to a reference plane.

The adjustment for a given height sample is derived as follows: consider a height sample S, of height h from the Earth's surface, and which is a horizontal distance d from the viewpoint V. Let the angle  $\theta$  be  $\angle SEV$  where E is the center of the Earth, and let R be the radius of the Earth. A point on the Earth's surface at  $\theta$  is  $R\cos\theta$  distant from E along the  $\overline{EV}$  radius, while the Earth's surface at V is R along the same radius. Therefore, the surface at V appears to be  $R - R\cos\theta$  lower than the surface at V. Subtracting this amount from R gives the apparent height R:

$$h' = h - (R - R\cos\theta). \tag{3.2}$$

To avoid computationally expensive trigonometric calculations, the  $\cos \theta$  term can be approximated with the first terms of the Maclaurin series of the cosine,  $1 - (\theta^2)/2$ .

$$h' = h - R\left(\frac{\theta^2}{2}\right).$$

The error introduced by this approximation is no larger than the product of R and the next term of the Maclaurin series,  $\theta^4/24$ . For a distance along the surface of 16 km, this is a maximum vertical error approximately equal to 0.01 mm. Because  $\theta = d/R$ , the equation can be rewritten as:

$$h' = h - \frac{d^2}{2R}.$$

Refraction has the effect of making the Earth appear to have less curvature by bending light and other EMR along the Earth's surface. This is represented by adding a coefficient n to the previous equation:

$$h' = h - n\left(\frac{d^2}{2R}\right). {(3.3)}$$

The value of n varies based on atmospheric conditions and the wavelength of the radiation; the value of 6/7 is typically used for visible light.

## 3.3.4 Integer Math

An interesting property of this approach to visibility is that it need not use floating-point arithmetic to maintain precision. The input heights can be represented using fixed-point numbers; for example, heights can be stored as an integral number of centimeters, rather than fractional meters. Horizontal distances are measured in terms of integral numbers of grid intervals. Slopes are stored as the ratio of these values. The output is calculated using Equation 3.1, where division by the denominator of m causes a single loss of precision due to integer division. This loss of precision will be less than a single unit of height. However, if the curvature correction described in the previous section is used, floating-point arithmetic may be required.

The implementation described later in this chapter showed little difference in performance between using fixed- or floating-point arithmetic, and fixed-point is used for the results shown in Section 3.4. Lack of floating-point arithmetic makes this approach well-suited for systems that lack FPUs.

### 3.3.5 Planar Sweep

Like van Krevald's algorithm, the approach in this chapter is based on a rotational planar sweep. Conceptually, the viewpoint and input DEM are projected onto the xy-plane, and a half-line is rotated around the viewpoint. This approach maintains a list of the interpolated values currently under the sweep line in the status structure. The status structure is updated when the sweep line crosses over DEM sample points. When the status structure changes, the change is called an event; the list of all events in the order they will be processed is the  $event\ list$ . The event list, the status structure, and how they are used, is described in more detail below.

**Event List:** First, an unsorted list of events is created. There is one event per height sample in the DEM, and each event is simply the row and column of the sample. Then, the samples are sorted based on their angle with the viewpoint, as shown in Figure 3.7. As before, avoiding expensive trigonometric functions will reduce execution time. Again, calculating the actual angle is

| 17 | 15 | 14 | 12 | 11 | 9  | 8  |

|----|----|----|----|----|----|----|

| 18 | 16 | 13 | 10 | 7  | 6  | 5  |

| 20 | 19 | V  | 1  | 2  | 3  | 4  |

| 21 | 22 | 23 | 24 | 25 | 26 | 27 |

Figure 3.7: In the event list, samples in the grid are ordered as they appear from the viewpoint, rotating counter-clockwise. Collinear samples, as with samples 1–4, are sorted by ascending distance from the viewpoint.

unnecessary. Instead, the cross product  $\overrightarrow{VA} \times \overrightarrow{VB}$  can be used to determine ordering, by calculating

$$(A_x - V_x) \times (B_y - V_y) - (B_x - V_x) \times (A_y - V_y).$$

If the result is positive, B is counter-clockwise from A; if the result is negative, B is clockwise from A.

The cross product alone cannot determine the ordering; there are several special cases to consider. First, the viewpoint divides the surrounding samples into four quadrants. A vector in the fourth quadrant is clockwise from a vector in the first quadrant, but the quadrants should be swept in order; that is, all events in the first quadrant should be swept before all events in the second quadrant, etc. The quadrant of any given sample can be determined by comparing the row and column indices of the samples with indices of the viewpoint. If they are in different quadrants, there is no need to calculate the cross product. Second, if the cross product is zero, then the samples are collinear with the viewpoint. In this case, the sample closer to the viewpoint is first in the event list ordering. As above, calculating the Euclidean distance, which requires calculating a square root, can be avoided by using the difference along the x- or y-axis to determine which sample is closer to the viewpoint.

In pvshed, this ordering logic is encapsulated in a *function object*, which is an object that can be called as though it were an ordinary function. In C++, function objects are instances of any class that overloads operator (). Function objects are frequently called *functors*, though they should

not be confused with the mathematical concept of the same name. The pvshed implementation of the sort described above uses a functor that stores the location of the viewpoint and can be used to compare two points to determine their ordering. The C++ STL provides several sorting functions that allow the use of user-defined functors for comparison, so pvshed is requires no additional sorting logic beyond that provided in the STL.

The viewshed area can be limited by omitting events from the initial, unsorted event list. One common example is restricting viewshed to a maximum visual radius. This can be accomplished by generating events for only the samples within the specified radius of the viewpoint, rather than for every sample in the input DEM. The rest of the algorithm remains unchanged.

## 3.3.6 Optimized Status Structure

The status structure holds a dynamically-maintained ordered list of the events as they occur along the sweep line. In most sweep algorithms, the status structure is some type of self-balancing binary search tree, such as a red-black tree, which allows updates and queries in logarithmic time. Self-balancing binary search trees have optimal asymptotic time complexities, but several factors can reduce the performance observed from real-world implementations of these data structures:

- 1. They are pointer-based: each node contains data and pointers to child nodes. The pointers inflate the size of the tree structure, making it less likely to fit into cache. Tree traversal is based on "pointer-chasing." It requires dereferencing a series of child pointers.

- 2. Their self-balancing behavior is not achieved without overhead. Additional data must be stored at each node to track tree structure, the structure must be checked whenever the tree is modified, and rebalancing operations occur whenever the tree becomes unbalanced.

- In most implementations, some kind of allocation or deallocation, such as the C++ new/delete

operations, are performed whenever adding or removing nodes to tree, adding additional

overhead.

The approach to determining visibility described above — checking for obstructions at grid lines — does not require a self-balancing binary tree. This is for three reasons:

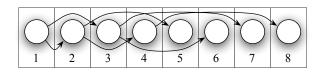

Figure 3.8: An implicit binary tree stores a tree structure in an array. The left child of node n is node 2n; the right child is node 2n + 1.

- 1. The size of the status structure can be determined before the sweep begins. As the sweep progresses, there will be an event one grid interval from the viewpoint, another event two grid intervals away, etc., up to the maximum distance from the viewpoint to an edge of the DEM. The maximum number of intervening points can be determined before the sweep starts: it will be the greatest component distance from the observer to an edge of the DEM. For example, given a 500×500 DEM and an observer at (200, 100), there will be at most 400 intervening points to store in the status structure, when the sweep line is oriented in the positive-y direction.

- 2. The shape of the status structure never changes. During the sweep, intervening points are never removed, only updated. Put another way, the position of an intervening point in the structure never changes. For example, for an intervening point five units aways from the observer, there will always be four other points between it and the observer.

- 3. The status structure can use integer keys. Rather than sorting the events based on a real-valued distance from the viewpoint, they can by sorted based on the number of grid intervals between them and the viewpoint. This number is always unique for each event, that is, there is always a single event one interval away, another two away, etc. Unique integer keys map naturally to array offsets.

For these reasons, a dynamic data structure is not required to handle variable amounts of data, nor to maintain ordering as points are added and removed. Instead, an implicit binary tree can be used. As shown in Figure 3.8, in an implicit tree, the location of the nodes determines parent/child relationships, rather than pointers. Because of this, the structure of the tree cannot change. However, parent and child nodes can be found with simple integer operations (right and left shift, re-

Figure 3.9: The new status structure is based on an implicit binary tree. Italic numbers are the index of the node in the underlying array. Bold numbers are leaf node indices. The internal nodes store the maximum slope over the indicated range of leaf nodes.

spectively), rather the dereferencing a pointer. Also, the implicit tree is optimally compact, because the nodes only store data, not keys or pointers.

The new status structure proposed here is built on top of an implicit binary tree is shown in Figure 3.9. The status structure records the index of the first leaf at initialization time. Notice that all the leaves are in a contiguous array, so any given leaf can be found by offsetting from the first. All intervening height samples are stored in the leaves, based on their distance (in grid intervals) from the viewpoint. Internal nodes store the maximum slope of all nodes in their subtree. Because is based on an implicit binary tree, the internal nodes must always form a complete binary tree. For trees with n leaves, there will be between n-1 and 2n-3 internal nodes.

Any time a leaf value is modified, the internal nodes must be updated as well. For example, consider modifying leaf 3. First the leaf value itself is changed at index 11. The slopes at leaves 2 and 3 are compared and the maximum is placed in their parent node at index 5. In the same fashion, that node is compared with its sibling, and its parent is modified; the process repeats in a bottom-up fashion until reaching the tree root at index 1. Modifying the tree is an  $O(\lg n)$  operation.

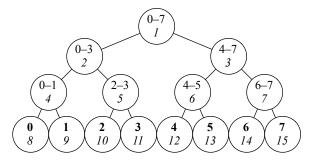

The internal nodes allow this data structure to act as an online variant of the *all-prefix-sums*, or *scan* operation. The scan operation takes a binary associative operator  $\oplus$  and an ordered list  $\langle a_0, a_1, \ldots, a_{n-1} \rangle$ , and returns the ordered list  $\langle I, a_0, (a_0 \oplus a_1), \ldots, (a_0 \oplus a_1 \oplus \cdots \oplus a_{n-2}) \rangle$ , where I is the identity element for  $\oplus$ . The scan operation is useful for determining visibility [97] where maximum serves as the  $\oplus$  operation, and the input list is the array of leaf values. The prefix of a

```

1: procedure PREFIX(tree, n)

t \leftarrow I

2:

i \leftarrow 2

3:

m \leftarrow 2^k

4:

while n \wedge (m-1) do

m \leftarrow m \div 2

6:

if m \wedge n then

7:

t \leftarrow \text{MAX}(t, tree[i])

8:

i \leftarrow i + 1

9:

end if

10:

i \leftarrow i \times 2

11:

end while

12:

return t

13:

14: end procedure

```

Figure 3.10: Finding the maximum slope before n in the status structure

leaf value is therefore the maximum intervening slope.

For example, to determine the visibility of a target point 6 grid intervals away from the view-point, the maximum slope of all intervening samples (0–5) is required. Figure 3.9 shows that node 2 holds the maximum slope of leaves 0 through 3, while node 6 holds the maximum of slope of leaves 4 and 5, so the maximum of values 0 through 5 can be found by taking the maximum of node 2 and node 6. As with van Krevald's algorithm, this is considering the left subtree each time the tree traversal chooses the right child. However, since there are no explicit child links, this is based on index arithmetic: each "1" in the binary representation of a node index corresponds to choosing the right child.

Figure 3.10 shows how to find the prefix of an arbitrary leaf n. If the tree is depth k, n has a k-bit binary representation. Let  $\wedge$  be the bitwise-and operation. The main loop examines one bit of n at a time, corresponding to a single level of the tree. At the beginning of each iteration, index i is at the left child of a node. The bitmask m is used to determine if the bit for this level is set, which is equivalent to choosing the right child. If so, the temporary value t is updated with the maximum of its current value and the left child value, and the index t is moved to the right child. At the end of the loop, t is moved to next left child. The loop condition at line 5 checks if there are any further bits set.

In line 2 a temporary value t is initialized with the identity element I. However, there is no identity element for maximum, i.e. there is no smallest slope. Instead, a near-vertical negative slope — for example the ratio -8000/1 can be used. In practice, this will be lower than any measured slope. This I value is also used to initialize all internal nodes of the status structure. Note that on line 3, the index of the first left child is initialized. The algorithm never checks the value at the root, because the maximum slope of all values in the tree is never required.

In contrast with the disadvantages of self-balancing binary trees listed above, this status structure is far more compact, has far less overhead during tree traversal, and has no overhead due to rebalancing or resource allocation. Updates and reads from the status structure are inside the inner loop of the rotational sweep algorithm described below. The advantages of the new status structure do not change the asymptotic runtime, but will reduce the measured execution time substantially. The reduced size of the status structure also means that it will fit in the cache of modern CPUs for any realistic viewshed problem.

# 3.3.7 Sweep Algorithm

After the sorted event list is created, viewshed analysis can proceed to the planar sweep. First, consider sweeping only the points in the octant from zero degrees up to 45 degrees from the viewpoint. In this octant, interpolation will always occur on y grid lines. Where the input DEM is w wide, begin by allocating a status structure large enough to hold  $w - V_x$  events, the number of gridlines from the viewpoint to the right edge of the DEM.

Figure 3.11 describes the sweep algorithm. The event list E is a sequence of n events,  $\langle E_0, E_1, \ldots, E_{n-1} \rangle$ . Each event is an (x,y) coordinate. G is the input DEM; the notation  $G(E_i)$  is the height recorded at the grid coordinates specified by  $E_i$ . R is the output raster of maximum obscured heights. S is the status structure. On line 6, the status structure is used to determine the maximum intervening slope. On line 7, the MAX-HEIGHT function uses Equation 3.1 to determine the maximum obstructed height at the location of  $E_i$  from the viewpoint V.

In most cases, when an event is processed corresponding to a height sample at (x, y), interpola-

```

1: procedure SWEEP(V, E, G, R)

Initialize status structure S

2:

3:

4:

for i \leftarrow 0 to n-2 do

5:

(x,y) \leftarrow E_i

slope \leftarrow PREFIX(S, x - V_x)

6:

R(E_i) \leftarrow \text{Max-Height}(V_z, slope)

7:

if COLLINEAR(V, E_i, E_{i+1}) then

8:

S[x-V_x] \leftarrow (G(E_i)-V_z)/(x-V_x)

9:

else

10:

while j \leq i do

11:

(x,y) \leftarrow E_j

12:

h \leftarrow \text{MIN}(G(E_i), G(x, y+1))

13:

S[x-V_x] \leftarrow (h-V_z)/(x-V_x)

14:

j \leftarrow j + 1

15:

end while

16:

17:

end if

18:

end for

R(E_i) \leftarrow \text{MAXHEIGHT}(S, G, E_{n-1})

19:

20: end procedure

```

Figure 3.11: Using the event list and status structure to implement the planar sweep

tion (using the minimum) is performed between that sample and at the sample at (x, y + 1). Using the interpolated height, the slope is calculated and inserted in the status structure at leaf  $x - V_x$ . However, when events are collinear with the viewpoint, for example P in 3.3(b), the sample value is used without interpolation. Line 8 checks for collinear points. The index j is used to track the next point requiring interpolation. When a series of collinear events are processed, j will lag behind; when the next non-collinear event is encountered, the while loop at line 11 will advance j to i while inserting the interpolated values.

The direction of interpolation depends on the location of the event relative to the viewshed. For example, events in the the octant between 0 and 45 degrees from the viewpoint will always interpolate in the positive-y direction as shown in Figure 3.11 and described in the previous paragraph. However, events in the next octant will interpolate in the negative-x direction. To avoid determining interpolation direction inside the sweep loop, the event list is partitioned before starting the sweep. Using a binary search, and the same functor used to sort the events, the events are

divided into eight octants. Because the events at octant boundaries are collinear, all values from a previous octant will be replaced at the boundary of a new octant, and the processing of each octant is completely independent.